# Perceive ERG0°2

## Perceive Ergo® 2 Edge AI Processor

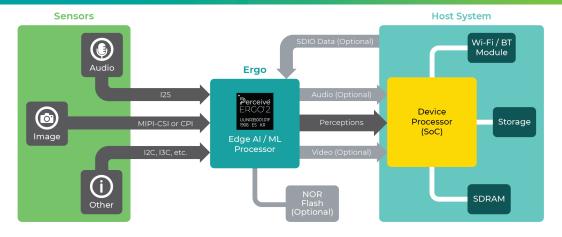

The Perceive® Ergo® line of edge AI processors delivers industry-leading power efficiency and enables sophisticated neural networks to run within power-constrained edge devices. With the new Ergo 2 processor, Perceive has improved on the breakthrough performance and power efficiency of Ergo. Ergo 2 is well-suited for on-device processing of neural networks like those used in advanced wearable devices, laptops, and cameras for security, action capture, or video conferencing.

## **Ultra power-efficient**

Ergo 2 is purpose-built for power-constrained devices. The chip requires substantially less power for typical workloads than its alternatives and importantly, it stays cool to the touch, which means it doesn't need additional cooling systems that take extra space and drain power resources. Ergo 2 uses no external DRAM and can handle many tasks without waking other processors in the device.

## **Enables more complex smart features**

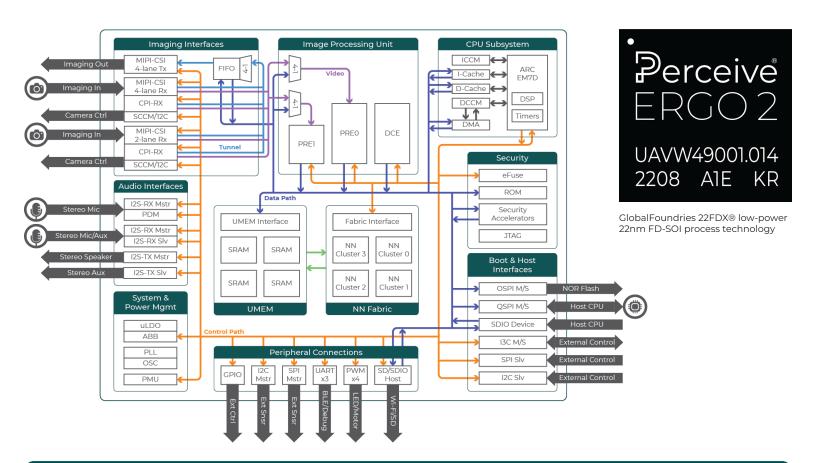

Ergo 2 offers a pipelined architecture and unified memory to improve its performance, flexibility, and overall operating efficiency. As a result, Ergo 2 can do more: supporting higher-resolution sensors, a wider range of neural networks, and multiple neural networks, including multiple heterogeneous networks in parallel.

## **Ready for integration**

Ergo 2 is ready to integrate and program. Perceive provides a suite of tools to support the development of products based on the Ergo 2 processor, including a comprehensive software development kit and the Percipio™ development platform, which optimizes neural networks for Ergo 2.

| Product Summary                 |                                   |                                       |                                                   |                                                               |

|---------------------------------|-----------------------------------|---------------------------------------|---------------------------------------------------|---------------------------------------------------------------|

| Name                            | Operating Voltage                 | Operating Frequency                   | Package                                           | Image Sensor<br>Resolution Support                            |

| Ergo 2<br>High Efficiency (HE)  | Core VCS: 0.8V<br>Core VDD: 0.65V | Fabric / CPU: 250 MHz<br>IPU: 333 MHz | 7mm x 7mm<br>FCCSP<br>144 Balls at<br>0.5mm pitch | 8 MP / 4K (4096 x 2160) @<br>30fps                            |

| Ergo 2<br>High Performance (HP) | Core VCS: 0.8V<br>Core VDD: 0.8V  | Fabric / CPU: 333 MHz<br>IPU: 433 MHz |                                                   | 12 MP (4096 x 3072) @ 30fps or<br>16 MP (4672 x 3506) @ 24fps |

## **Features and Specifications**

#### **Neural Network Fabric**

- Supports wide range of neural network architectures, multiple neural networks, multiple sensor data types (ex., video, audio) concurrently.

- New Architecture in Ergo 2 enables enhanced neural network job pipelining

- Enhanced fabric instruction set with improved compression and activation functions

- · Native attention / transformer support

#### **Unified Memory Architecture**

- Concurrent access to SRAM from Neural Network Fabric & Microprocessor AMBA bus

- Flexible usage mapping between Neural Network Fabric, CPU, & other data sources / sinks

- Enables virtual to physical memory mapping, resulting in enhanced job pipelining

- · Enhanced performance and memory efficiency

#### **Security**

- Secure boot including authentication and decryption of embedded software and neural network assets

- ECDSA and AES hardware acceleration of authentication and decryption for rapid application load times

- True Random Number Generator (TRNG) for key exchange

## **Image Processing Unit (IPU)**

- · Dual, simultaneous image processing pipelines

- » Pipeline 1 (PRE1) supporting four Regions of Interest and max. input image size of 16MP (4672 x 3506) RAW @ 24fps

- » Pipeline 0 (PRE0) supporting single Region of Interest and max. input image size of 3MP (2048 x 1536) RAW @ 60fps

- Input image formats supported: RAW (Bayer pattern), RGB, Y-only, YCC444, YCC422, YCC420. All formats are supported at 8/10/12/14 bits.

- Output image formats supported: RAW planar, Y-only, YCC444 / RGB planar, YCC422 planar, YCC420 planar. 8 / 10 / 12 / 14 bits for RAW format & 8 bits for RGB & YCC.

- Supported functions: Black-level compensation, Color correction, Histogram computation, Clipping pixel data, RGB to YCC conversion, Cropping, Downsampling (Average and Bilinear), Gamma correction, Scaling, Dynamic range compression, Rotation, Translation, Demosaicing, Distortion Correction, Lens shading correction

#### **External Memory & Storage Support**

- Octal/Quad SPI NOR Flash, 8MB to 256 MB for boot firmware and applications

- eMMC or SD NAND memory for applications and persistent data storage

- Optional memoryless boot and application provisioning from a host processor

#### Microprocessor

- · ARC EM7D RISC / DSP processor

- 32x32 register file, 256 KB / 256 KB instruction / data closely-coupled memories

- · 32 KB / 32 KB instruction / data caches

- · Floating point unit (FPU)

- Integrated 16-channel DMA, interrupt controller, 32-bit timers (x2), watchdog timer, and real-time counter

- · Hardware Action points & performance monitor

- · Enhanced security package:

- » Four privilege levels: Secure / Normal + Kernel / User

- » Secure Memory Protection Unit (MPU)

- » Stack checking

- » Secure debug

- DSP functions:

Trigonometric & square-root accelerators, Fractional datatype support, Complex / Butterfly operations, vector operations, saturation / rounding operations, 32 x 32 MUL / MAC unit

#### **Other System Features**

- Integrated Ultra-Low Dropout Regulator for simplified low-power hibernate mode

- · Two integrated PLLs for system & MIPI-Tx freq.

- · Integrated low-power crystal oscillator (20-25MHz)

- 1 kbit eFuse array for customizable operating modes and security keys

\*Bolded items are new features in Ergo 2

## **Ports and Interfaces**

## **Imaging Interfaces**

- MIPI CSI-2 Rx 2.5Gbps 4-lane input

(refer to Dreduct Suppose 4-lane)

- (refer to Product Summary table for supported resolutions)

- · MIPI CSI-2 Rx **2.5Gbps** 2-lane input video data (FHD/1080p @ 60fps max)

- MIPI CSI-2 Tx **2.5Gbps** 4-lane video tunneling output

- · 2x 10-bit Camera Parallel Interfaces (CPI) (FHD/1080p @ 30fps max)

- · 2x SCCM/I2C Master Camera Control ports

## **Data and Storage Connections**

- · SD/eMMC/SDIO:

- SD NAND Flash devices, eMMC NAND Flash devices, SDIO Wi-Fi devices

- UART: Bluetooth Low Energy (BLE) devices

## **Audio Interfaces**

- · 2x I2S Master Rx ports for two stereo microphone inputs

- · I2S Master Tx port for audio output

- $\cdot$  I2S Slave Rx port for auxiliary audio input

- · I2S Slave Tx port for auxiliary audio output

- · PDM port supporting up to four audio channel input

## Boot and Host Interfaces

- · SD/SDIO Device supporting Host boot / inference interface

- · Octal/Ouad SPI Master/Slave interface

- » Supports NOR flash boot (master) or Host boot / inference interface (slave)

- » Supports SDR and DDR transactions (Master only)

- · Quad SPI Master/Slave

- » Supports Host boot/inference interface (Slave)

- » Supports SDR and DDR transactions (Master only)

- SPI Slave

- · I3C Master/Slave (shared with sensor interface), I2C Slave

- UART

#### **Sensor and Control Interfaces**

- · SPI Master

- · I3C Master/Slave (shared with host interface) and I2C Master

- · UART

- · GPIO: Up to 53x 1.8V GPIO pins and up to 8x 3.3V/1.8V GPIO pins

- · PWM: Up to 4 programmable outputs